PrimEx Data Acquisition Rates

12/11/01

D. Lawrence

Introduction:

The goal of this document is to describe rate capabilities of the DAQ which will be implemented for PrimEx. In particular, what we might expect for deadtime and event rates.

Based on earlier trigger simulation studies, the trigger rate expected, under ideal conditions, is less than 30Hz with a 100% trigger efficiency. It is assumed we can always lower the discriminator thresholds to increase the event rate and regain any efficiency lost due to the "less than ideal" conditions of the actual experiment. This being the case, we are then limited by what is considered an acceptable deadtime. For PrimEx, we need a very low deadtime in order to achieve the statistical goals of the experiment with the beam time awarded.

DAQ rate limitations:

There are three places which might limit the DAQ rate:

Conversion: The digitization time taken by the fastbus module

Readout: The time it takes to read the data into the ReadOut Controller (ROC)

Transfer: The time it takes to transfer the data from the ROC to the host Unix system over the ethernet.

Each of these is now discussed below. We'll assume a 2 kHz DAQ rate and that each T-counter is firing at 2MHz where needed.

Conversion Time:

The conversion times for the three types of Fastbus modules which will be used in the PrimEx DAQ are given in the table below.

We will use one 1877 TDC module for HYCAL and a number of them for the tagger E-counters. The tagger also uses an 1877S and two 1872A's for the T-counters.

The 1872A TDC's are used

for the high resolution timing of the left and right PMTs of the

tagger T-counters. They have a full range of 820ns. The number of

hits a single T-counter will see per event is given by:![]() .

This gives a total conversion time for each of the 1872A TDCS of

.

This gives a total conversion time for each of the 1872A TDCS of

![]() .

.

|

Fastbus Module |

Conversion Time |

|---|---|

|

LRS 1877 TDC

|

750 nsec + 50 nsec per hit within the programmed full scale; 1.6 µsec minimum |

|

LRS 1877S TDC

|

1.2 µsec + 50 nsec per hit within the programmed full scale; 1.75 µsec minimum |

|

LRS 1872A TDC

|

2.5 µsec for each channel that is stopped ("hit") + 10 µsec (taken from LRS 1875A specs.) |

|

LRS 1881M ADC

|

12 µsec for all 64 channels in 13-bit mode, 9 µsec of all 64 channels in 12-bit mode |

The 1877S TDC is used for

the tagger T-counter LR coincidence signals and for the pair

spectrometer. The maximum, full range is![]() ,

but we may need to limit this and/or the number of hits per event in

order to maintain a reasonable event size. The number of hits a

single T-counter channel will see, on average, in

,

but we may need to limit this and/or the number of hits per event in

order to maintain a reasonable event size. The number of hits a

single T-counter channel will see, on average, in![]() is

is

![]() .

The total conversion time for the module would then be

.

The total conversion time for the module would then be

![]() .

The pair spectrometer rates will be about a factor of 10 smaller than

the T-counters so they will not dominate the conversion time of the

crate.

.

The pair spectrometer rates will be about a factor of 10 smaller than

the T-counters so they will not dominate the conversion time of the

crate.

The maximum discriminator rate expected from HYCAL is on the order of 50 kHz so it too will be a relatively small conversion time.

The 1881M ADC modules

will each have a

![]() conversion

time.

conversion

time.

The conversion time of

the 1872A modules dominate the total conversion time of all systems

in the DAQ. If we were to exclude these high resolution TDCs and rely

purely on the 1877's, we'd reduce the total conversion time by a

factor of 10 to the

![]() needed

by the 1881M ADC's.

needed

by the 1881M ADC's.

Readout Time:

The CODA/Fastbus system

can be run in one of two modes, buffered and un-buffered. The

buffered mode takes advantage of the multiple-event buffering

available on many Fastbus modules (including all those which we plan

to use for PrimEx). When using buffered mode, the Trigger Supervisor

is allowed to send another trigger as soon as all modules have

completed the conversion phase. Un-buffered mode requires the readout

phase to complete before another trigger can be accepted. Since the

readout phase can be as long as

![]() ,

deadtime can be significantly reduced using buffered mode.

,

deadtime can be significantly reduced using buffered mode.

Using buffered mode, the

readout time can still become a factor if the event rate is large

enough that the mean time between triggers becomes comparable to the

conversion time plus readout time. In a worst case scenario, this

would be

![]() .

This would correspond to a rate of about 2.3 kHz. Once the buffers

gets filled up, the Trigger Supervisor would be forced to wait for

the end of the readout phase before taking another event. The

deadtime would reflect this condition by suddenly jumping from 30% to

100%.

.

This would correspond to a rate of about 2.3 kHz. Once the buffers

gets filled up, the Trigger Supervisor would be forced to wait for

the end of the readout phase before taking another event. The

deadtime would reflect this condition by suddenly jumping from 30% to

100%.

The important point here is that we will run in unbuffered mode and the readout time will not be a factor. We must only ensure that our event rate is low enough to maintain a reasonable deadtime (<10%).

Transfer Time:

The transfer time is really only a limitation when we approach the 1Gbit ethernet line speed. The JLab online group has stated that this should not be a concern provided we stay at around 1MB/sec or less per fastbus crate. In practice, G6c ran in the summer of 2001 with data rates as high as 8 MB/s from the TAGE crate.

For the ADC's the

built-in pedestal suppression will limit the number of 32-bit words

per event to less than 100 (each of the two photons hitting the

calorimeter will reach at most, about 36 detectors). This will give

as an upper limit,

![]() .

This rate will be shared between two fastbus crates.

.

This rate will be shared between two fastbus crates.

For the T-counter TDC's

we assume a![]() time

range, as above. This gives, on average, 2 hits per counter, per

event. The tagger E-counter TDC's reside in the same fastbus crate.

Since the E-counters overlap by 1/3, there will be 2 E-counter hits

for each T-counter hit 50% of the time and 1 E-counter hit for the

other 50% of the time. This gives

time

range, as above. This gives, on average, 2 hits per counter, per

event. The tagger E-counter TDC's reside in the same fastbus crate.

Since the E-counters overlap by 1/3, there will be 2 E-counter hits

for each T-counter hit 50% of the time and 1 E-counter hit for the

other 50% of the time. This gives

![]() E-counter

hits per T-counter hit on average. The pair spectrometer will

contribute

E-counter

hits per T-counter hit on average. The pair spectrometer will

contribute

![]() p.s.

hits/Tcntr hit.

p.s.

hits/Tcntr hit.

The total data rate for the TAGE crate will then be:

![]()

This rate can always be cut down by turning off part of the tagger's focal plane.

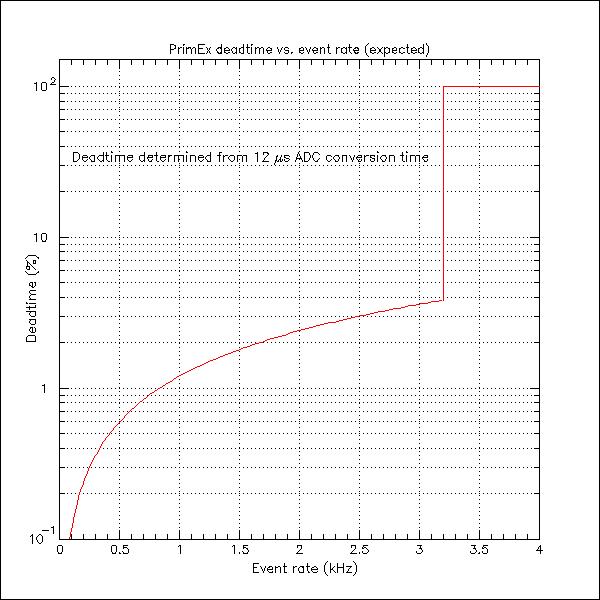

Deadtime:

Using buffered mode, the

deadtime will be determined solely by the conversion time of the

slowest module. If the high resolution 1872 TDC's are excluded, the

module with the longest conversion time is the 1881M ADC. This has a

conversion time of

![]() .

Using this, the deadtime as a function of rate is a simple linear

relation shown in the plot below. The worst-case-scenario cutoff at

3.2 kHz was determined by assuming a

.

Using this, the deadtime as a function of rate is a simple linear

relation shown in the plot below. The worst-case-scenario cutoff at

3.2 kHz was determined by assuming a![]() readout

time. Shorter readout times will only push that cutoff to higher

event rates.

readout

time. Shorter readout times will only push that cutoff to higher

event rates.

Conclusions:

![]() We should, if at all possible, exclude the high precision 1872 TDC

modules since their long (and non-constant) conversion time would

increase our deadtime by more than a factor of 10.

We should, if at all possible, exclude the high precision 1872 TDC

modules since their long (and non-constant) conversion time would

increase our deadtime by more than a factor of 10.

![]() Without the 1872 TDC's the deadtime is determined by the 1881M ADCs

and should be less than 2% at a 1 kHz event rate.

Without the 1872 TDC's the deadtime is determined by the 1881M ADCs

and should be less than 2% at a 1 kHz event rate.

![]() Information from the tagger's 1877/1877S multi-hit TDCs will

dominate the data stream. The estimates above show that it should be

within the limits of the DAQ system's capabitilies which were tested

during G6c. This estimate, however, is based on limiting hits to

a

Information from the tagger's 1877/1877S multi-hit TDCs will

dominate the data stream. The estimates above show that it should be

within the limits of the DAQ system's capabitilies which were tested

during G6c. This estimate, however, is based on limiting hits to

a![]() range.

range.