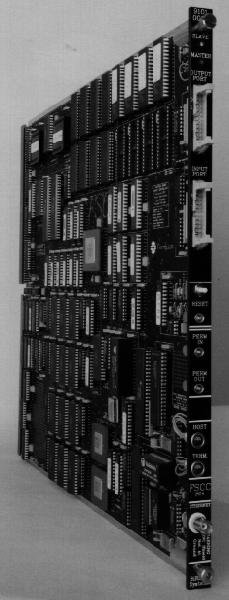

MODEL 9101

FASTBUS SMART CRATE CONTROLLER (FSCC), PC4a & PC4b

with Real-Time Operation System (R.T.O.S) Software Support

FEATURES

APPLICATIONS

GENERAL DESCRIPTION

FSCC is a single-width FASTBUS module designed to be a medium performance read-out controller which reads data from FASTBUS and outputs it through an auxiliary port. It performs most FASTBUS operations but is not intended to be a general-purpose FASTBUS master. A Motorola 68020 processor is used to control operation of the module by memory-mapped instructions. Any features which are not time-critical are relegated to software. The VxWorks operating system, resident monitor, module diagnostics and control software for the Ethernet and serial ports are implemented in EPROM. User code may be placed in the second EPROM bank or in RAM.

The low-level operation of the various hardware ports (FASTBUS, auxiliary, serial, Ethernet) is by dedicated controllers. The FSCC operates as a master on both the FASTBUS crate segment and on the non-FASTBUS auxiliary port. To maximize throughput, high speed block transfer data from FASTBUS to the auxiliary output port is routed through a DATA FIFO that can hold up to 512 events, limited only by the 4K physical memory depth of the FIFO and the 512-event depth limit of the control FIFO. When used in concert with the trigger FIFO card upgrade, this means that the FSCC can be successfully used with multi-event-buffering FASTBUS Slaves, where the triggers can be decoupled from the actual data readout.

FASTBUS MASTER

The FSCC can perform pipe-lined transfers at the rate of 100, 200, and 400 nsec per word; and block transfers at the rate of approximately 150 nsec per word. The FASTBUS master port is implemented by routines which are micro-encoded into a high speed sequencer. These routines are triggered by "move" instructions from a user program running on the MC68020 processor. Standard and assured access arbitration of the FASTBUS is supported. The processor may load a list of FASTBUS instructions in the LIST FIFO, and then the FASTBUS sequencer will execute that list upon receipt of an "execute list" instruction from the processor. The list has a "re-execute" command and a "wait for trigger" command, allowing simple readout sequences to be entirely controlled by the list sequencer and requiring no processor intervention.

FASTBUS SLAVE

Geographical address recognition logic is contained in hardware. All other slave selections are controlled by the MC68020 processor. Thus any FASTBUS CSR or DATA locations can be defined by processor software. FASTBUS WT is asserted on each DS transition. The data cycle response time is dependent of software and is typically 10-15 msec per FASTBUS word.

ETHERNET INTERFACE

Ethernet is interfaced to the MC68020 CPU through an Intel 82586 Ethernet controller and a dual-ported memory. The dual-ported RAM speeds up both systems as the CPU does not release the bus each time a DMA occurs. The CPU is interrupted when a command is finished or a message is received.

DATA OUTPUT PORT

The data from FASTBUS read operations is delivered to the output port. The output port is a buffered 4K by 32bit FASTBUS data FIFO, 32 bit wide TTL interface to a FASTBUS auxiliary card. The separately acquired auxiliary card provides interconnect protocol as required by the user. Currently, auxiliary cards are available for RS-485 (Bi Ra Models FBA-771 & FBA-791) and can be transferred to a VME Readout Buffer module (RBUF-Bi Ra Model 1700), and possibly a fiber optic card soon.

PC4b

OVERVIEW

The primary goal of the PC4B modifications were to change the FSCC to allow it to meet the newly revised DART (Data Acquisition Real Time) Interface Specification (Document Number: ESE-DART-950511-A). The DART Interface Specification defines the physical medium, data format, and timing of the RS-485 data stream, PERMIT_IN/PERMIT_OUT token passing links, and the Event Trigger Link.

Secondary goals of the PC4B changes were to enhance data flow control by routing the Data FIFO status flags into the Trigger Hold-Off Output logic, and to fix two design flaws.

DART Interface Specification Changes

Data Link Changes (OPORT)

Most of the changes required to meet the DART Data Link Specification, actually involved changes to the auxiliary card (FSCC-DARTAC). However, there were some changes to the FSCC itself. The timing of the enable lines to the RS-485 drivers on the FSCC-DARTAC was changed to enable the driver for the Data Strobe line 50ns before the drivers for the data lines. This was done to help prevent false Data Strobe transitions due to crosstalk on the data cable. The OPORT controller was also changed to prevent data transitions for 100ns after the data drivers are enabled.

Supported OPORT modes have been redefined to more realistically reflect the way the OPORT is actually used. The designation Event_Mode has been renamed Token_Middle. Force_Event_Mode is now known as Token_First, and Event_EOR is now Token_Last.The name changes are to more accurately reflect the function of the modes, and hopefully, to make programming the FSCC somewhat more intuitive.

Token_Only mode has been added to allow the use of the PC4b as the only data source on a data link. With previous versions of the FSCC, it was sufficient to set the OPORT into Event_Mode (now ), and use a LEMO type terminator installed in the PERMIT IN input. This effectively forced the PERMIT_IN input true. With the conversion of the PERMIT_IN input to NIM level, putting a terminator into the PERMIT_IN input does not force the input true, therefore, the new mode was needed.

CPU mode (Control mode) operation of the OPORT is no longer supported. CPU mode allowed data to be written directly into the Control FIFO, and output as data through the OPORT. This mode was originally thought to be useful for testing the personality cards, and the data links connected to them. However, it has become obvious that writing data directly into the Data FIFO is much more useful for testing purposes. To make space in the OPORT controller for Token_Only mode, the seldom-used CPU mode was deleted.

Event_With_Manual_Permit_Out and Permit_Out modes are also no longer supported. These modes were originally designed to allow the readout program to drive End_Of_Record. It is now driven with the appropriate timing when the OPORT is set into Token_Last mode. Once configured, the readout code no longer needs to be concerned about the communications protocol on the data link.

The RS-485 driver for the End_Of_Record signal is now enabled whenever the OPORT is set into Token_Last or Token_Only modes. The driver is disabled in all other modes.

The FSCC-DARTAC was changed to allow the Data Strobe pulse to be inverted and lengthened to match the DART Data Link Specification. The active edge is now the low going edge of the Data Strobe. All termination SIP resistor packs were removed from the FSCC-DARTAC to allow the use of DART Upstream and Downstream termination modules, and unused control lines 16/32*, SSTROBE, FEVEN, SPARE0, SPARE1, and SPARE2 were either cut or permanently disabled.

The function of the four DIP switches on the FSCC-DARTAC have been redefined. Switches 1, 3, and 4 now have no function and can be left in either the open or closed position. Switch 2 now controls the RS-485 WAIT enable. When the switch is open, RS-485 WAIT is disabled. WAIT received from the data buffer is ignored. When the switch is closed, WAIT is enabled. WAIT received from the buffer is passed to the FSCC and the data transmission is paused. This switch setting was added to allow the RS-485 cables to be disconnected and still allow data to be clocked out of the OPORT for testing purposes.

PERMIT Link Changes (PERMIN/PERMOUT)

The most significant change to the front panel PERMIT connectors is that they were changed to NIM level signals from TTL level signals. The active level for both PERMIT_IN, and PERMIT_OUT, is a NIM "1", which approximately -0.8 Volts when the line is terminated in 50 ohms. The inactive level is NIM "0" which is approximately ground level. The FSCC's PERMIT_IN connector supplies the necessary 50 ohm NIM termination.

In order to use the FSCC as the only data source a data cable, the module must think that it is both "first" and "last" on the PERMIT token passing chain. It must be first so that it starts outputting data without waiting for a PERMIT_IN on the first event, and it must be last so that it drives the EOR signal on the data cable. With previous versions of the FSCC, "first and last" mode was done by setting the FSCC into "last" (Event_EOR) mode, then putting a 50 ohm terminator into the PERMIT_IN input on the front panel. The terminator forced the PERMIT_IN input to its active state, so the module always had the token. Since the PERMIT connections were changed to NIM levels on the PC4b FSCC's, inserting a 50 ohm terminator into the PERMIT_IN input no longer forces the input to its active state. To allow the PC4b modules to be both "first and last" in the PERMIT chain, a new mode was added to the Output Port Controller. When using the PC4b FSCC as the only data source on the data cable, Force_Event_EOR (first and last) mode should be used.

Trigger Link Changes (Trigger Strobe, and Trigger ID bits)

The RS-485 Trigger Strobe input on the PC4b FSCC has been changed slightly. The active edge of the RS-485 Trigger Strobe has been changed to the low-going edge. The termination resistors have been removed from both the RS-485 Trigger Strobe and the Trigger ID inputs. An external termination module must now be used. A NIM level version of the Trigger Strobe input was also added to the PC4b FSCC which is logically ORed with the RS-485 Trigger Strobe input. This input is also on the front panel.

The Trigger Hold Off (THO) front panel output has been changed from a TTL level signal to a NIM level signal. The active level for all front panel NIM level signals is a NIM "1" (approximately -0.8 Volts when terminated by a 50 ohm resister).

DATA FLOW CONTROL ENHANCEMENTS

Originally, the FSCC was not designed with multi-event buffering front-end modules in mind, for the simple reason that they did not exist at that time. Since it was desired to use the FSCC with these newer front-end modules, the Trigger FIFO and the Trigger Hold Off (THO) output was added to the FSCC during the PC4a upgrade. In an effort to prevent data buffer overflow when the FSCC is used with these modules, two of the FSCC's Data FIFO status flags have been added to the THO logic. Data FIFO Half Full, and a latched version of Data FIFO Full have been logically ORed with the jumper selectable THO condition available on the Trigger FIFO child board. If the Data FIFO becomes half full during a readout, the THO output is driven true until the Data FIFO becomes less than half full. If the Data FIFO becomes full during a readout, this error condition is latched by the THO output and is driven true until the Output Port Controller is reset.

BUG FIXES

Two bugs have been corrected in the PC4b modifications. The first involved skewing of the FASTBUS Data Acknowledge (DK) signal. The FASTBUS specification dictates that the Master must delay the incoming DK signal from the Slave by a small amount, to allow some setup time for the Slave Status (SS) lines. Previous versions of FSCC's did not have this delay, and it was noticed that there were rare but persistent problems with the FSCC when used with certain slaves. The DK input of PC4b FSCCs now provide this delay.

The second bug is related to the FASTBUS Short Timer time-out Value. The Short Timer is the device which times the response of the Slave or Ancillary Logic to the Master's assertion of certain control lines. Previous versions of the FSCC had a Short Timer time-out value of approximately 1.6 micro-seconds which is the minimum allowed by the FASTBUS specification. It seems that some Ancillary Logic had Broadcast timers of approximately the same value. This caused occasional time-out errors during Broadcast addressing cycles. The time-out value of the Short Timer on the FSCC was increased to prevent this error.

During testing of certain front-end modules which featured Mega-Block mode readout, it was noticed that the readout worked without errors until a certain number of modules were added to the Mega-Block chain. This caused a Short Time-out error on the FSCC. This problem was traced to the way the Slaves released the AS-AK lock after the Mega-Block readout was completed. The release of AK had to ripple back through all of the Slaves before the AK line on the bus was lowered. Each of the Slaves added some delay, until the total AS(down) to AK(down) time was greater than the newly lengthened Short Timer value on the FSCC. Since the current FASTBUS specification is somewhat vague with regard to this condition, it was decided that lengthening the FSCC's Short Timer value even more was the most cost effective solution. The PC4b Short Timer value is approximately 3 micro-seconds.

SOFTWARE

The real-time multi-tasking operating system supported is VxWorks by Wind River Systems, and code created by Fermilab for the FSCC hardware implementation. Of course any operating system can be utilized with the understanding that the end user develops their own programs. All information required to program the FSCC is provided.

A second bank of EPROM is provided to contain user programs which may run independently of, or use services (e.g. serial port driver) provided by the operating system.

STANDARD CONFIGURATION:

1M Bytes 0 wait static RAM and 2MB of 1 wait state EPROM

POWER REQUIREMENTS:

+5.0 Volts6 Amps |

-5.2 Volts2 Amps |

-2.0 Volts0.2 Amps |

WEIGHT:

3 lbs.

ACCESSORIES:

OPTIONS:

-12M Bytes 0 wait static RAM and 2MB of 1 wait state EPROM |

-24M Bytes 0 wait static RAM and 2MB of 1 wait state EPROM |

Note:4M SRAMs are now available but require software modifications. |