# Hall B 12GeV Upgrade Workshop

Jefferson Lab 2-3 February 2007

# **ELECTRONICS** for the Upgrade

R. Chris Cuevas Jefferson Lab Physics Division Group Leader -- *Fast* Electronics

Topics:

Requirements Projects and Progress 250Msps Flash ADC Energy Sum Module The Bigger Picture DAQ/Electronics Work Plans All Halls using JLAB Electronics Concerns & Issues

### DAQ & Trigger Motivation

- New Electronics are a result of new requirements

- These requirements are extracted from Technical Design Reviews and of course direct discussions with Hall Staff.

- To achieve upgrade requirements for increased Trigger rates and DAQ data rates:.

- Replace FastBus 1881 modules -- Slow conversion [1.2uS]

- Design 'pipeline' front end readout modules that will eliminate delay cable for each channel, and incorporate signal processing features, trigger processing, and event buffering [Flash ADC]

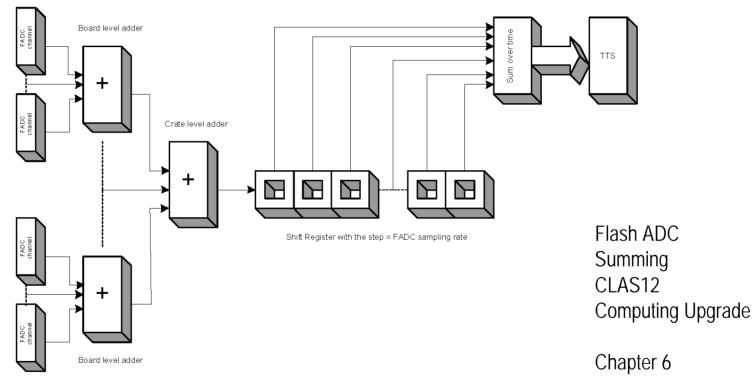

- Design ADC 'summing' system to be used in Level 1 Trigger

Requirements

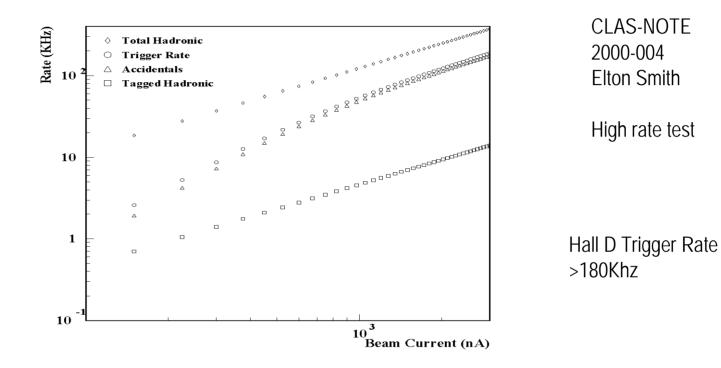

Figure 7.2: Estimated rates as a function of electron beam current. Plotted is the total hadronic rate and the estimated trigger rate, which is the sum of accidental coincidences and the tagged hadronic signal.

Requirements

### DAQ & Trigger Motivation

#### Requirements

# Flash ADC Status - Prototype

### Block Diagram

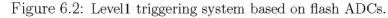

This diagram is not intended for extreme details, and has not been updated recently. The diagram shows the important decisions for FPGA selection and other hardware features.

• <u>Schematic</u>

The Schematic is a tremendous amount of effort and is 47 pages!! Clearly the work of several engineers and designers.

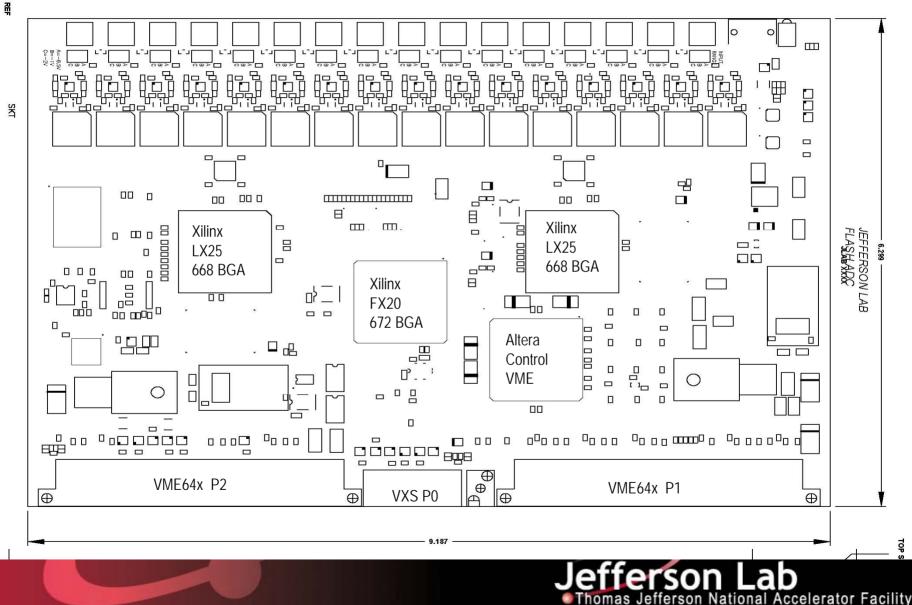

Printed Circuit Board

The latest layout is shown on a slide that follows. Power regulators and other power components will be finalized soon and full time work for routing will begin soon.

<u>Components</u>

XC4VFX20 parts ordered and received. These parts have all 8 MGT units operational at 3.125Gbps. 10 bit Maxim ADC parts ordered and received. XCLX25 parts have been received. All other parts are stock items and we will purchase enough for two prototype units.

FlashADC\_BlockDiagram

3/31/2006

#### fADC250

#### VME64x Flash ADC Module Specifications

|                   | VME64x Flash ADC Module Specifications |                                                                                                                                          |                                                                                                                                                                                                                                                  |  |

|-------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                   |                                        |                                                                                                                                          |                                                                                                                                                                                                                                                  |  |

|                   | Signal Inputs                          | Number<br>Range<br>Offset                                                                                                                | 16 S Version (50 Ohm, LEMO)*<br>-0.5V, -1V & -2V. User Selectable<br>±10% FS per channel via DACs                                                                                                                                                |  |

|                   | Clock                                  | Sampling<br>Jitter<br>Source                                                                                                             | 250 MSPS, Differential<br>1 pS (10-bit ADC), 350 fS (12-bit ADC)<br>Internal and External                                                                                                                                                        |  |

| 13<br>12<br>11    | Control<br>Inputs/Outputs              | Clock<br>Trigger<br>Status 1<br>Status 2<br>Sync                                                                                         | IN – Diff., LVPECL (Front Panel & Backplane)<br>IN, OUT - Differential (Front Panel & Backplane)<br>OUT – Differential (Front Panel & Backplane)<br>OUT – Differential (Front Panel & Backplane)<br>OUT – Differential (Front Panel & Backplane) |  |

| 5<br>5<br>5<br>5  | Conversion<br>Characteristics          | 00                                                                                                                                       | VSoftware Strobe (Internal)<br>10-bit (8 and 12-bit by chip replacement)<br>± 0.8 LSB<br>± 0.5 LSB<br>56.8 dB @ 100 MHz Input<br>cy 32 nS                                                                                                        |  |

|                   | Trigger Latency 8 μS                   |                                                                                                                                          |                                                                                                                                                                                                                                                  |  |

| $  \cdot \circ  $ | Tigger Latency 6 µ6                    |                                                                                                                                          |                                                                                                                                                                                                                                                  |  |

| 6                 | Data Memory                            | 8 μS                                                                                                                                     |                                                                                                                                                                                                                                                  |  |

|                   | Data Processing                        | rocessing Sparcification<br>Windowing<br>Charge, Pedestal, Peak<br>Time (Over Threshold, Relative to trigger)<br>Output (Backplane, VXS) |                                                                                                                                                                                                                                                  |  |

| °250 ℃            | Interface                              | VME64x – 2eVME Data Transfer Cycles (40, 80, 160 & 320 MB/sec) with VXS-P0                                                               |                                                                                                                                                                                                                                                  |  |

|                   | Packaging                              | 6U VME64x                                                                                                                                |                                                                                                                                                                                                                                                  |  |

|                   | Power                                  | +3.3V, +5V, +12V, -12V                                                                                                                   |                                                                                                                                                                                                                                                  |  |

|                   | FJE JLAE FADC_SPEC.DOC                 |                                                                                                                                          |                                                                                                                                                                                                                                                  |  |

#### **ADC FPGA Functional Description**

The ADC FPGA receives streaming 12 bits data at 250 MHz from 8 ADC. It performs **Channel Data Processing** for each ADC, computes **Energy Sum** of all ADC, and generates **Acceptance Pulse** for each ADC. The data selected in Channel Data Processing and results of Energy Sum are passed to VME FPGA and Hit Sum FPGA respectively for further processing.

#### 1. Channel Data Processing:

# ADC Data

**Trigger Input**

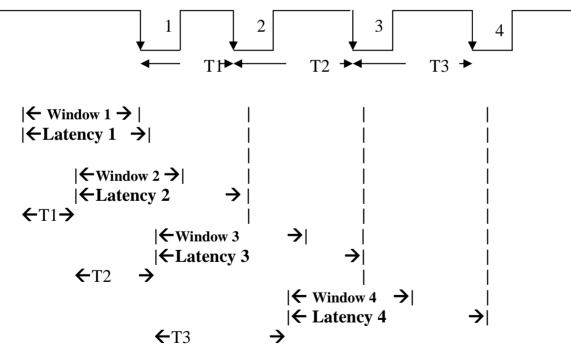

Time Line

|←Programmable Trigger Window→| ------ 100nS to 2uS ------

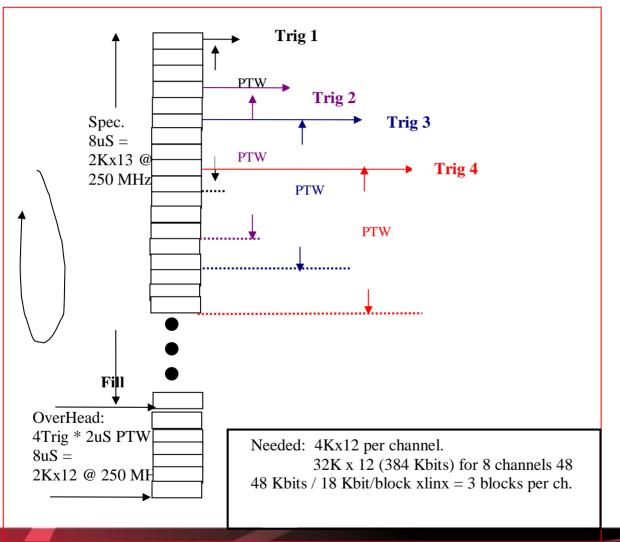

Data from ADC are stored continuously in circular buffer until Trigger input becomes active (low). The data that was stored from the time that the Trigger occurs back to the time specified by Programmable Latency within the Programmable Trigger Window are processed. There are three options to which these data are processed. The options are selectable by the user. While data are being processed, ADC FPGA will continue storing incoming ADC data with no loss of data.

4 Data Readout 'Options' Available

#### **Trigger Input Buffer:**

In the event that the Trigger Input rate is faster than the data processing time, the processing algorithm has to be able to process 4 (or more. TBD due to memory limitation) consecutives triggers with no loss in time lines. If a trigger cannot be processed due to an overflow condition, the VME FPGA will be notified: "no data for trigger". The format is TBD.

Minimum T1 is 50 nS (less will be loss).

### Successive Trigger Input Illustration:

#### Memory Model for Successive Trigger Input Illustration:

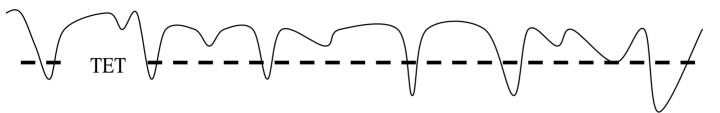

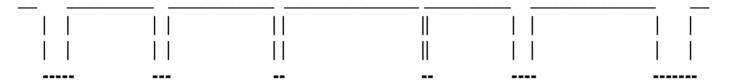

### **Acceptance Pulse Illustration:**

ADC data

### Hit Bit

Additional feature is the energy sum for all 16 input channels

The energy sum value is continuously updated ever 4ns

Jefferson Lab Thomas Jefferson National Accelerator Facility NEWPORT NEWS, URGINIA UNITED STATES DEPARTMENT OF ENERGY FLASH ADC FJB,ELI,HD,JW 6/23/06

FJB,EJ,HD,JW 6/23/ MADE IN THE U.S.A.

FAB FAB1

### 14 Layer circuit board Power/GND layers not shown **ENORMOUS AMOUNT OF WORK!**

찙

FAB FAB1

Jefferson Lab Thomas Jefferson National Accelerator Facility NEWPORT NEWS, VIRGINIA UNITED STATES DEPARTMENT OF ENERGY FLASH ADC FJB,EJ,HD,JW 6/23/06 MADE IN THE U.S.A.

# Flash ADC Development Milestones

- This module is a very challenging design and the progress is remarkable, given that the design team members are committed to other projects also.

- > October 2006 -- Design Complete [ Schematic reviewed]

- November '06 February 2007 Final layout/Routing/Review/Order

- ➢March 2007 June 2007 INTENSE TESTING! This will include software development work for Coda 'Drivers' and Test Station.

- Summer 2007 Production modules,, "How many would you like to order?"

# Energy SUM Module Development

- The prototype module is assembled and initial testing is complete. The design engineer left the lab in August, and the work focus has been on the Flash ADC, but FPGA code design for the sum module has recently been tested.

- The energy sum prototype module will allow us to continue the research necessary to gain expertise with the new VXS, { VME with serial extensions} technology.

- We have purchased the necessary test instruments for measuring the MultiGigabit Transceivers, and have evaluated several VXS crates from different manufacturers.

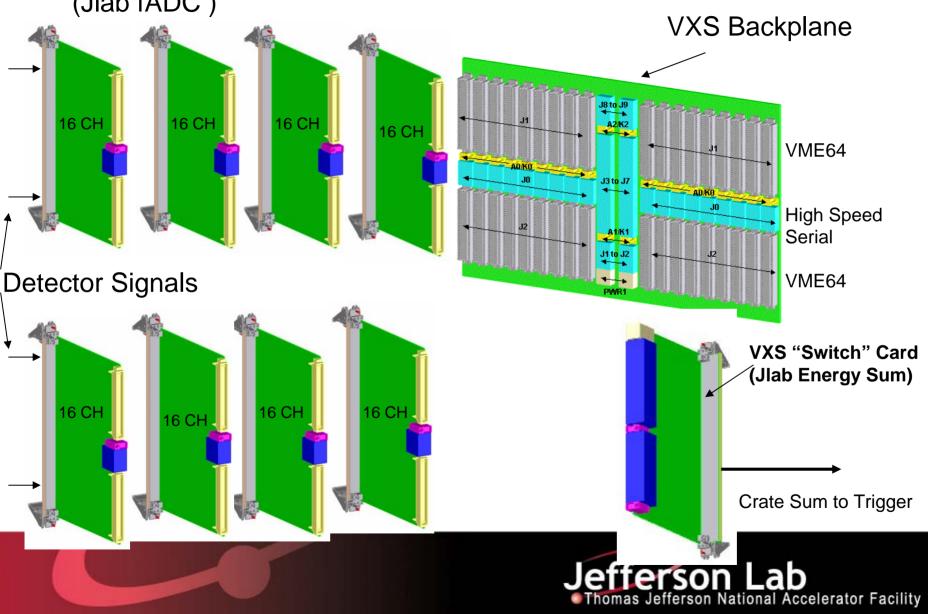

# Quick VXS Review

## Why VXS?

VXS provides an infrastructure for multi-GBps switched serial technologies to compete and grow on top of VME

Expected to extend the life of VME for decades

Part of the VME Renaissance

Pro's

Very high bandwidth

Low latency

Increased scalability (as compared to a bus architecture)

Less contention (as compared to a bus architecture)

Experiment with switched serial under the safety of the parallel bus

Migrate from parallel bus to serial switched at one's own pace

Provides a platform for high availability systems – hot swap

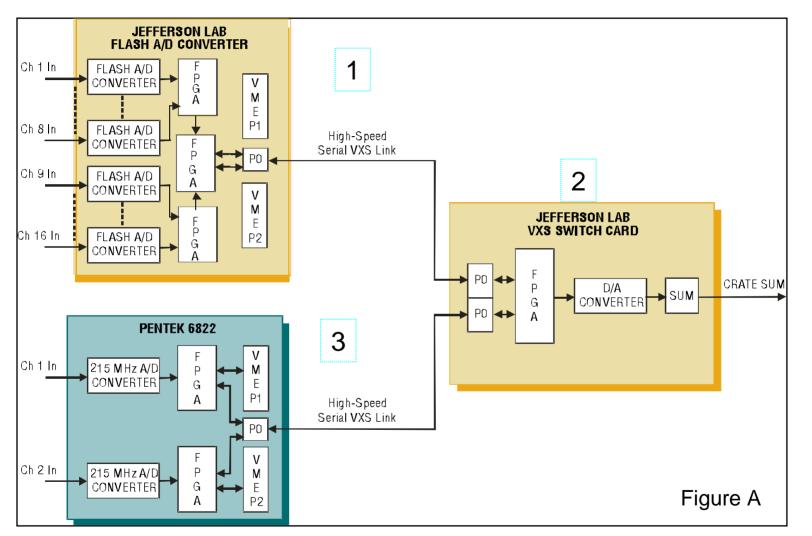

### Flash ADC, Energy Sum & VXS

# **Quick VXS Review**

VXS "Payloads" (Jlab fADC)

# More VXS Fun

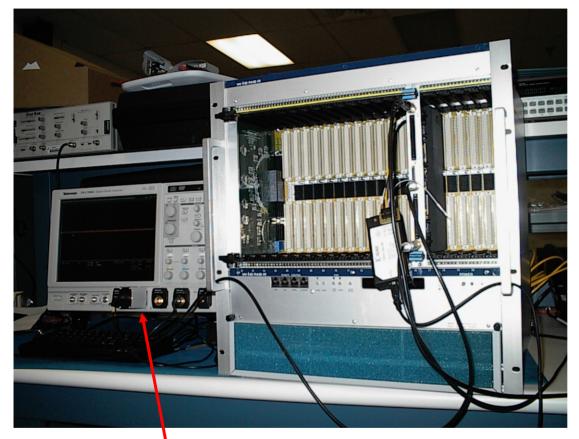

21 Slot VXS crate Manufactured by Wiener Plein & Baus

The absolute latest In high speed serial Analysis with digital Oscilloscope technology Was delivered in Sept!

Tektronix DSA 70000 8Ghz BW Digital Serial Analyzer

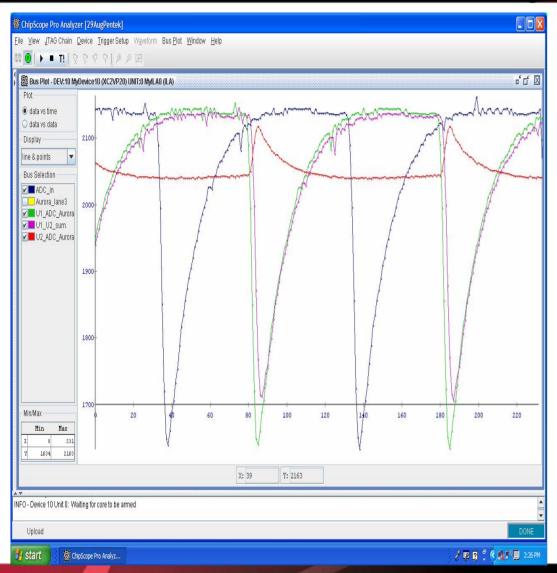

#### Figure 3: VXS Loopback Waveform results (Xilinx ChipScope Pro)

Test Conditions:

Input ADC1: BLUE  $\rightarrow$  Negative exponential pulse

Input ADC2: RED  $\rightarrow$  Negative exponential pulse; Inverted and attenuated (14db) 1Mhz Input Frequency for both inputs Output ADC1\_Aurora: GREEN  $\rightarrow$  Data transmitted round trip for ADC1 Output ADC1\_ADC2\_SUM: MAGENTA  $\rightarrow$ ADC1 + ADC2 result transmitted round trip **Conclusion:**

The backplane functions correctly for the given payload assignment. Four high speed serial 'lanes' are used at 2Gbps for an aggregate transfer rate of 8Gbps. The Aurora protocol appears to have a latency of approximately 400ns roundtrip, but the proper summing function occurs without error and is extremely stable.

Further testing with the Pentek module is planned to achieve the maximum serial transfer rating of the Xilinx VirtexII Pro FPGA. The Jlab switch slot design will allow the testing of two Jlab flash ADC prototype

modules and the Pentek module.

# The Bigger Picture

- DAQ & Electronics Work Plans

- All Halls using JLAB Electronics

- Concerns & Issues

### **DAQ & Electronics Work Plans**

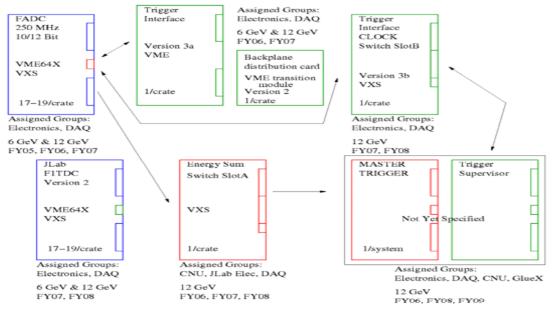

Figure 1: Schematic of the electronic boards that are required to support the plans for GlueX pipeline electronics and data acquisition. Indicated are the module classifications, responsible groups, expected use in the 6 or 12GeV program, and estimate of time frame for design and prototyping.

4

\*Note: Two Xilinx development Modules received for CNU to Prototype and test crate summing Information to Master Trigger

- ~ Discussion ~

- Upgrade requirements demand increase in performance of existing DAQ/Front-End Electronics

- We are in a decent position to develop the required instrumentation modules to replace aging and obsolete modules. (F1TDC replaces 1872, FlashADC replaces 1881 and analog summing )

- Designs for new 'pipeline' trigger interface modules are in close collaboration with the DAQ/Coda group

- Concerns & Issues

- New technology, New test equipment, More firmware (Fpga), More power per module, Software design,,,

- The elusive final requirements document. Maybe a better idea is to form working groups for these custom designs,,

- Manpower

- Money