## Program for the Hardware Interlock System of the Hall C Neutral Particle Spectrometer

Peter Bonneau, Mary Ann Antonioli, Aaron Brown, Pablo Campero, Brian Eng, George Jacobs, Mindy Leffel,

Tyler Lemon, Marc McMullen, and Amrit Yegneswaran

Physics Division, Thomas Jefferson National Accelerator Facility, Newport News, VA 23606

September 8, 2021

A program to monitor and interlock the Neutral Particle Spectrometer (NPS) is being developed. This note summarizes the features of the program.

The NPS hardware interlock program runs on the Linux real-time operating system of a NI CompactRIO (cRIO) 9045 controller. This program does not require an Ethernet network connection or a user interface. To remotely monitor the sensor signals [1, 2], an Ethernet network connection to the controller is available as an option.

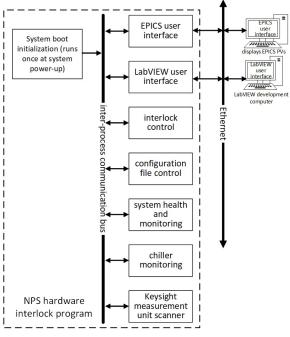

The eight subroutines of the hardware interlock program are shown in Fig. 1 and listed in Table I. Subroutines 1–6 are similar to that of the interlock systems developed for the SVT, Forward Tagger, and RICH I [3, 4, 5, 6, 7, and 8], which have been reliably monitoring and protecting the detectors since 2015. Subroutines seven and eight, chiller monitoring and Keysight unit scanner, are unique to the NPS interlock system.

Subroutine system boot initialization runs once, upon cRIO controller power-up, and initializes the hardware interlock system program; interlock trip thresholds previously saved before system power-down are restored during initialization.

Operating as a server, the *EPICS user interface* subroutine translates the signals into EPICS process variables (PVs) and transmits them to the Ethernet network subnet connected to the controller. These PVs communicate with EPICS user interface programs installed and running on computers that are on that subnet.

The *LabVIEW user interface* subroutine is a communication link between the hardware interlock program running on the cRIO controller and the LabVIEW user interface program running on a LabVIEW development computer. Used by system experts for data analysis, hardware maintenance, and code updates, the user interface has controls and signal monitoring capability. Many features, e.g. controls for signal averaging, are restricted to the LabVIEW interface program.

FIG. 1. Diagram of subroutines of the hardware interlock system program and their communication connections.

Data acquired from the Keysight are continuously compared with interlock trip thresholds; the *interlock control* subroutine initiates a trip when any of the monitored signal values are outside pre-defined limits. Depending on which signal causes the trip, either the CAEN high voltage power supply, the chillers, or both could be disabled. The CAEN power supply and the AC units powering the chillers have local indicator lights indicating the status of the interlocks.

| # | Subroutine Name            | Function                                                                        |

|---|----------------------------|---------------------------------------------------------------------------------|

| 1 | System boot initialization | Initializes hardware interlock program; runs once upon system power-up          |

| 2 | EPICS user interface       | Interfaces interlock system to EPICS; translates signals to and from EPICS PVs  |

| 3 | LabVIEW user interface     | Expert level control and monitoring; independent from EPICS                     |

| 4 | Interlock control          | Evaluates signals vs. pre-defined thresholds; takes corrective action if needed |

| 5 | Configuration file control | Controls storage and readback of thresholds; file is stored on cRIO SD card     |

| 6 | System health monitoring   | Monitors cRIO system health, including heartbeat and cRIO status                |

| 7 | Chiller monitoring         | Monitors status of chillers for crystal zone and electronics zone               |

| 8 | Keysight unit scanner      | Controls acquisition of data from sensors located within detector               |

TABLE I. Summary of main subroutines for the NPS hardware interlock system program.

When a new interlock trip threshold is entered, the *con-figuration file control* subroutine writes the value to a file located on the SD card installed in the cRIO controller. This subroutine is used during system commissioning to construct the configuration file.

Subroutine *system health monitoring* checks the status of the cRIO controller and the interlock program, as well as the percentage of CPU usage, memory usage, and the system uptime. Additionally, a signal is generated to indicate whether the cRIO controller and interlock program are active.

The chiller status and temperatures from the electronics and crystal zones, as well as the coolant flow, temperature, and pressure, are read by the *chiller monitoring* subroutine.

The  $\sim 180$  sensors in the system are connected to a Keysight 34980A multifunction switch and measurement unit. The *Keysight unit scanner* subroutine controls the acquisition and readout of the data from the measurement unit.

In conclusion, a network-independent, LabVIEW program is being developed to monitor and interlock the NPS. Many facets of this program are similar to those developed for other hardware interlock systems. Chiller monitoring and reading of the Keysight scanning system are two new features.

- [1] P. Bonneau, et al., *Hardware Interlock System for the Hall C Neutral Particle Spectrometer* DSG Note 2021-15, 2021.

- [2] P. Bonneau, et al., *Sensors for the Hall C Neutral Particle Spectrometer*, DSG Note 2020-35, 2020.

- [3] M.A. Antonioli, et al., *The CLAS12 Silicon Vertex Tracker*, Nucl. Instrum. Methods Phys. Res. A 962 (2020).

- [4] P. Bonneau, et al., *Hardware Interlock System of the Hall B Silicon Vertex Tracker*, DSG Note 2016-04, 2016.

- [5] A. Acker et al., *The CLAS12 Forward Tagger*, Nucl. Instrum. Methods Phys. Res. A 959 (2020).

- [6] P. Bonneau, et al., *Interlock System for the Hall B Forward Tagger*, DSG Note 2017-07, 2017.

- [7] M. Contalbrigo, et al., *The CLAS12 Ring Imaging Cherenkov Detector*, Nucl. Instrum. Methods Phys. Res. A 964 (2020).

- [8] M.A. Antonioli, et al., *Proposal for RICH Hardware In*terlock System, DSG Note 2017-01, 2017.