## **EIC DIRC Laser Interlock PCB Netlist Check**

Marc McMullen 2023-06

This week I started the final design checks for the EIC DIRC Laser Interlock printed circuit board. This process involves careful checking of the design routing and component placement to reduce the chance of a problem when the board returns from the manufacturer. The primary issue would be a circuit shorted to another circuit or plane.

After the review and all engineering changes are completed and reviewed again, I performed a netlist check on the boards 68 nets. Nets refer to a circuit of connected component pins or pads. Nets can have as few as two connections or more. For instance, the ground net for the EIC DIRC Laser Interlock board has 72 connections. A net with that many connections is usually power or ground and typically has a copper plane. I produced a spreadsheet of all the nets and connections. The spreadsheet has columns to verify the connection status of the nets to the planes and pads. I then check all the nets individually.

| Netlist |             |      |          |          |             |               |        |        |        |         |         |

|---------|-------------|------|----------|----------|-------------|---------------|--------|--------|--------|---------|---------|

|         |             |      |          |          |             |               | Plane  |        |        |         |         |

| NODE    | REFERENCE   | PIN# | PIN NAME | PIN TYPE | PART VALUE  | Net connected | 5V PWR | 5V GND | 24 PWR | 24V OUT | 24V GND |

|         |             |      |          |          |             |               |        |        |        |         |         |

| [00001] | Sweep-Intlk |      |          |          |             |               |        |        |        |         |         |

|         | U2          | 12   | Н        | INPUT    | CD74HC30E   | Υ             | N      | N      | N      | N       | N       |

|         | U6          | 16   | 1Q       | OUTPUT   | SN74LS75N   | Υ             | N      | N      | N      | N       | N       |

| NODE    | REFERENCE   | PIN# | PIN NAME | PIN TYPE | PART VALUE  | Net connected | 5V PWR | 5V GND | 24 PWR | 24V OUT | 24V GND |

| [00002] | Sweep-Input |      |          |          |             |               |        |        |        |         |         |

|         | D37         | 1    | A        | PASSIVE  | BAT46       | Υ             | N      | N      | N      | N       | N       |

|         | D38         | 2    | K        | PASSIVE  | BAT46       | Υ             | N      | N      | N      | N       | N       |

|         | J17         | 2    | 2        | PASSIVE  | Sweep input | Υ             | N      | N      | N      | N       | N       |

|         | U6          | 2    | 1D       | INPUT    | SN74LS75N   | Υ             | N      | N      | N      | N       | N       |

| NODE    | REFERENCE   | PIN# | PIN NAME | PIN TYPE | PART VALUE  | Net connected | 5V PWR | 5V GND | 24 PWR | 24V OUT | 24V GND |

| [00003] | Status      |      |          |          |             |               |        |        |        |         |         |

|         | J23         | 1    | 1        | PASSIVE  | Status      | Υ             | N      | N      | N      | N       | N       |

|         | J24         | 1    | 1        | PASSIVE  | Status      | Υ             | N      | N      | N      | N       | N       |

|         | U3          | 3    | 1Y       | OUTPUT   | CD74HC32E   | Υ             | N      | N      | N      | N       | N       |

|         | U4          | 2    | 1A       | INPUT    | SN74HC02N   | Υ             | N      | N      | N      | N       | N       |

| NODE    | REFERENCE   | PIN# | PIN NAME | PIN TYPE | PART VALUE  | Net connected | 5V PWR | 5V GND | 24 PWR | 24V OUT | 24V GND |

| [00004] | Reset       |      |          |          |             |               |        |        |        |         |         |

|         | D27         | 1    | A        | PASSIVE  | BAT46       | Υ             | N      | N      | N      | N       | N       |

|         | D28         | 2    | K        | PASSIVE  | BAT46       | Υ             | N      | N      | N      | N       | N       |

|         | J16         | 1    | 1        | PASSIVE  | Reset       | Υ             | N      | N      | N      | N       | N       |

|         | J16         | 2    | 2        | PASSIVE  | Reset       | Υ             | N      | N      | N      | N       | N       |

|         | J25         | 1    | 1        | PASSIVE  | Reset       | Υ             | N      | N      | N      | N       | N       |

|         | J26         | 1    | 1        | PASSIVE  | Reset       | Υ             | N      | N      | N      | N       | N       |

|         | U4          | 6    | 2B       | INPUT    | SN74HC02N   | Υ             | N      | N      | N      | N       | N       |

Fig. 1. Netlist check spreadsheet with the first four nets shown

- Made a netlist file using excel to use as a reference for checking the PCB net connections

- Completed netlist check by verifying the connection of all nets

## **EIC DIRC Laser Interlock PCB Netlist Check**

Figure 1 shows the first four nets of the EIC DIRC Laser Interlock netlist check. The first net (Sweep\_Intlk) is highlighted. It has two connections, U2 pin 12 and U6 pin 16. The columns on the right indicate that it is connected at both pads and not connected to any planes.

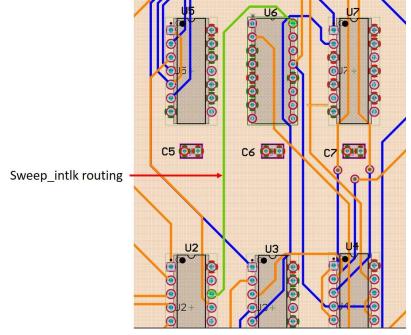

Figure 2 shows the routed connection between U2 pin 12 and U6 pin 16. In addition, both pads are inside a red circle which indicates that they do not connect to the power plane. Checking the connection to all planes requires cycling through the layers.

In conclusion, I have started checking all the nets for the EIC DIRC Laser Interlock PCB design. After the netlist check is complete, a final design rule check is done by the Altium software to make sure there are no errors. If the DRC has no errors, I will start making the manufacturing files. The files get sent to the PCB manufacturer to make the boards.

Fig. 2. The Sweep\_Intlk net on the top layer is highlighted in green.