# **EPICS: CSS-Phoebus**

#### Peter Bonneau

2023-09

### **EPICS Alarm System in Phoebus**

I am developing an EPICS alarm system based on CS-Studio Phoebus. Phoebus will be used for new EPICS system development and will replace the existing applications using ALH for alarms and MEDM for monitoring and control screens. Phoebus will also be used to replace Eclipse-based CS-Studio applications.

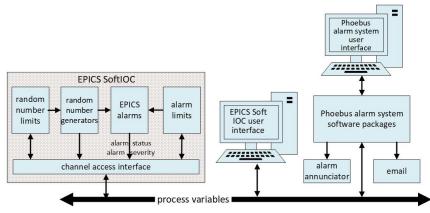

For stand-alone development of the Phoebus alarm system (<u>DSG Note</u> <u>2021-37</u>), a test system has been designed, developed, and implemented. Consisting of a host-based EPICS softIOC acting as detector signal simulator (DSG Notes <u>2023-23</u> & <u>2032-32</u>), and a Phoebus software development system, the Phoebus alarm test station (Fig. 1) has successfully been used to demonstrate the proof of concept (<u>DSG Note</u> <u>2023-06</u>) of the Phoebus alarm system using simulated data.

For the next phase of development, a test of the Phoebus alarm system is being developed using live data. As opposed to the simulated detector data that is generated via the host-based EPICS softIOC, a live data test would show how the alarm system actually reacts in an experimental environment. The alarm system should respond to the live data the same way it does for the simulated detector data.

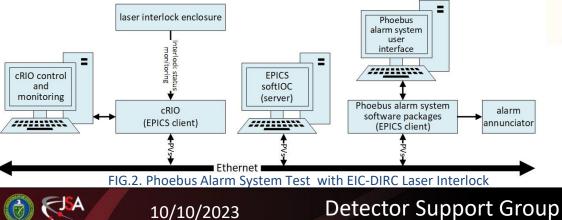

The Phoebus alarm system beta testing using live data will use the EIC-DIRC laser interlock PCB (<u>DSG Note 2023-01</u>) as the signal source. A test setup has been designed to monitor the laser interlock status signals on the PCB. The test setup (Fig. 2) consists of a National Instruments cRio which monitors the laser interlock status signals, an EPICS softIOC which generates the alarms, and the Phoebus alarm system which monitors for alarm conditions.

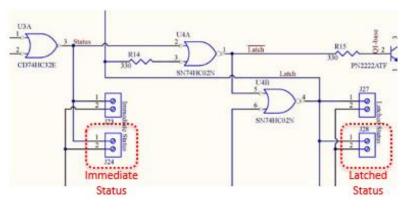

The signals *immediate status* and *latched status* sourced by the laser interlock PCB (Fig. 3) will be monitored by the test. The *immediate status* signal is the instantaneous laser interlock status value which will then latch

- Developing CS-Studio Phoebus based controls, monitoring, and alarm system

- Developing an Phoebus alarm system test with the EIC-DIRC laser interlock

### **Detector Support Group**

## **EPICS: CSS-Phoebus**

the *latched status* signal. The latched signal requires operator intervention to reset the signal and enable the laser. A high TTL signal level on the status signals indicate that the laser is disabled.

An ADC module within NI cRio model 9045 controller chassis will digitize the status signals. A program developed in LabVIEW and running on the cRio's Linux real-time operating system reads the digitized laser interlock status data from the ADC. Acting as an EPICS client, the cRio converts the status data into an EPICS process variable (PV) and writes it to the network using EPICS channel access.

An EPICS softIOC application developed for the Phoebus alarm system test functions as the EPICS server for the system. The softIOC also compares the laser interlock status PV values with the preprogramed alarm limits stored within the softIOC. If the PV value equals or exceeds the alarm limits, the softIOC generates an alarm via PV alarm status (HIHI, HIGH, LOW, LOLO) and severity (major, minor).

Code developed for the Phoebus alarm system software packages specifically for this test with the EIC-DIRC laser interlock will monitor the interlock status PVs for alarm conditions. If the Phoebus alarm system detects a PV in an alarm state, it latches PV value at the time of the alarm and a timestamp. The alarm system alerts users of PV alarms via the user interface developed for this test. The annunciator also alerts the user via an audible alarm. Additionally, the acknowledgement of alarms and the configuration of the alarm settings is accessed via the user interface.

FIG.3. EIC-DIRC Laser Interlock PCB Signals