## The Backplane Board of the Hardware Interlock System for the Second Ring Imaging Cherenkov Detector

Marc McMullen, Mary Ann Antonioli, Peter Bonneau, Aaron Brown, Pablo Campero, Brian Eng, George Jacobs,

Mindy Leffel, Tyler Lemon, and Amrit Yegneswaran

Physics Division, Thomas Jefferson National Accelerator Facility, Newport News, VA 23606

October 29, 2021

The backplane board inside the hardware interlock chassis, developed for the second ring imaging Cherenkov (RICH) detector, connects the 24 SHT35 sensor boards—each populated with two sensors that measure both humidity and temperature inside the electronics panel and nitrogen volume of the RICH detector—to the reconfigurable I/O mezzanine card (RMC) in the hardware interlock chassis [1, 2].

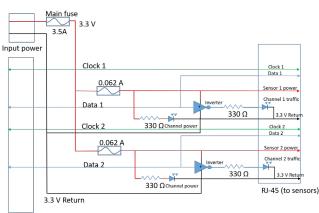

Molex connectors on the 24 SHT35 sensor boards connect by ~65' long, CAT 7 cables to the RJ-45 connectors on the backplane board, which is the interface between the RMC and the SHT35 sensor boards. Figure 1 shows the schematic for the connection between the backplane board and the two SHT35 sensors on the sensor board.

P1 (from RMC)

FIG. 1. Connection schematic from backplane board to SHT35 sensor board.

Each sensor power line on the backplane board has a 0.062-A fuse connected to the 3.3-V input power line. Each fuse has an LED to indicate its power status. To indicate signal activity, on the backplane board each sensor signal line has an LED powered by a Texas Instruments SN74LVC1G04 inverter chip that is on the data line. All the LEDs have resistors to limit current.

The backplane board has four routing layers (Top, Inner\_1, Inner\_2, and Bottom) and two plane layers (power and ground). In the board's stack-up, each routing layer is adjacent to a plane layer, which provides a return path for the signal traces. The smallest trace size, used for the signal traces, is 8 mils, the smallest clearance, between the pads of the inverter chips, is 6 mils. The board's dimensions are 14.5" x 4".

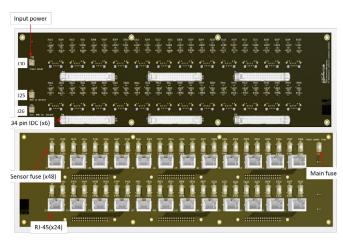

The top of the backplane board, Fig. 2, has two rows of 34-pin IDC connectors, three per row, each connected to four RJ-45 connectors on the bottom of the board. There are two rows of RJ-45 connectors, 12 per row; the top row (J1–J12) is for the electronic panel sensors, the bottom (J13–J24) for the nitrogen volume sensors.

FIG. 2. Top (upper) and bottom (lower) of backplane board.

The IDC connectors mate to 34-pin ribbon cables, which connect to 34-pin IDC connectors on the RMC. Each IDC connector passes sixteen sensor signals from the backplane board to the RMC.

The 0.1" header J30 on the top provides input voltage of 3.3 V from an external supply. For the input voltage, a fuse, main fuse, is on the bottom of the board, where it can be accessed from the back of the chassis. The two 0.1" headers J25 and J26 can be used to connect the ground plane to the copper plane on the bottom layer of the board. J25 is to be used during testing, J26 will be wired to a connector on the chassis back panel. The shields of the RJ-45 connectors connect to the bottom plane.

The backplane board design has been completed and sent for manufacturing. Five boards will be manufactured.

- [1] Marc McMullen, et al., Sensirion SHT-35 Sensor Board Design for Hall B's RICH II Detector, DSG Note 2021-14, 2021.

- [2] Marc McMullen, et al., Design of the Reconfigurable Input/Output Mezzanine Card for the Hardware Interlock System of Hall B's Second Ring Imaging Cherenkov Detector, DSG Note 2021-22, 2021.